Dans la course à la miniaturisation continue des processeurs, Samsung vient de prendre l’avantage sur ses concurrents. Le poids lourd sud-coréen de l’électronique grand public annonce ce 30 juin 2022 le début de la production de la prochaine génération de puces, doublant au passage l’Américain Intel et le Taïwanais TSMC, deux rivaux également engagés dans cette compétition.

L’annonce de Samsung tourne autour de la génération des puces dont la finesse de gravure atteint 3 nanomètres. À cette échelle, l’épaisseur d’un cheveu apparaîtrait colossale : un nanomètre est une fraction infime d’un mètre (un milliardième) et un cheveu est 50 000 fois plus épais. Aujourd’hui, les puces les plus avancées sur le marché sont annoncées à 5 et 7 nanomètres (nm).

50 000 fois plus petit que l’épaisseur d’un cheveu

Le géant asiatique ne tarit pas d’éloges pour décrire le saut qualitatif. Par rapport au 5 nm, ce premier processus pour le 3 nm « permet de réduire la consommation d’énergie jusqu’à 45 %, d’améliorer les performances de 23 % et de réduire la surface de 16 % ». Et avec processus de seconde génération, les gains sont de 50 %, 30 % et 35 %, respectivement.

Les progrès réguliers dans la haute ingénierie informatique ont pour effet de donner l’impression de renvoyer les précédentes déclarations en la matière à des années-lumière de nous. Souvenez-vous : en 2017, IBM se félicitait de savoir graver des puces avec une finesse de 5 nm. Cinq ans plus tard, ce niveau de gravure est devenu tout à fait banal.

On trouve ainsi cette finesse de gravure chez Apple (M1, M2, A14 Bionic, A15 Bionic…) Qualcomm (Snapdragon), Samsung (Exynos), HiSilicon (Kirin), Nvidia (Grace Hopper), mais aussi AMD ou MediaTek. Aujourd’hui, des smartphones et des ordinateurs sont couramment équipés de composants qui bénéficient des avancées dont se félicitait IBM.

Le calendrier de déploiement de cette nouvelle classe de microprocesseurs n’est pas détaillé dans l’annonce de Samsung, mais c’est probablement en 2023 que l’on assistera à cette bascule. Le temps d’atteindre une production de masse à un rythme industriel, afin d’alimenter les chaînes de production qui assembleront les composants futurs des ordinateurs et des smartphones.

Jouer sur la géométrie des transistors

Il faut noter que le degré de miniaturisation est devenu à ce point extrême que les différentes annonces ne rendent pas tout à fait justice aux avancées qui ont lieu depuis quelques années. Les termes comme 3 nm, 5 nm, 7 nm, mais aussi quelques seuils au-dessus, ne désignent plus tant une taille, mais une certaine technologie et une certaine forme géométrique dans la conception.

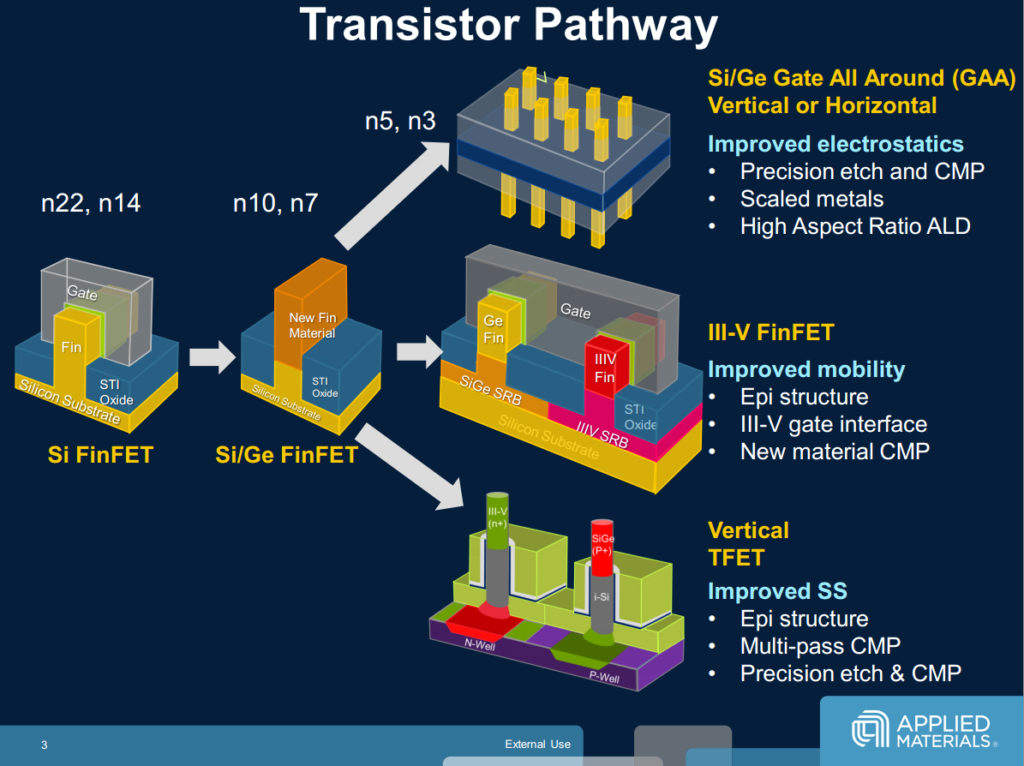

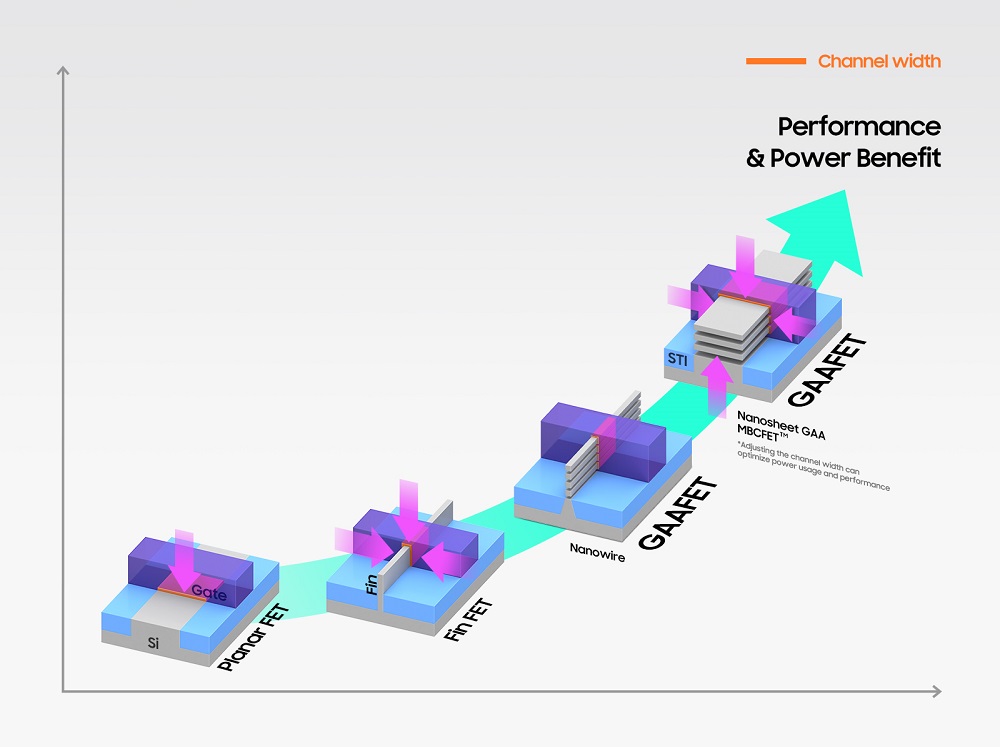

Ainsi, Samsung s’appuie sur une technique appelée « GAAFET » et une solution maison nommée « MBCFET ». Pour qui ne suit pas l’actualité des processeurs de près, ces acronymes sont obscurs. Il faut noter qu’à partir des années 2010, des processeurs « en trois dimensions » ont commencé à voir le jour, en opposition aux technologies traditionnelles, « plates ».

Le secteur a ainsi commencé à transitionner vers la solution FinFET (fin field-effect transistor), soit transistor à effet de champ à ailettes. Ce procédé, qui a transformé la géométrie des transistors, a servi pour la génération 14 nm, 10 nm et 7 nm. Puis est arrivée la méthode « GAAFET » (gate-all-around) pour descendre sous le seuil du 7 nm, en particulier le 5 nm.

Le GAAFET est un dérivé du FinFET, mais en l’appliquant en quelque sorte partout — d’où son nom de portail tout autour, pour signaler la présence de plusieurs portes pour laisser passer le courant électrique dans les transistors — mais la difficulté est que tout est devenu si petit qu’il y a des fuites d’électrons. D’où des travaux sur la géométrie des transistors désormais, plutôt que sur leur taille.

Avec le GAAFET, le canal de conduction se réduit à un nanofil, détaillait en 2019 Olivier Faynot, chef du service au Commissariat à l’énergie atomique (CEA) dans le laboratoire d’électronique et de technologie de l’information. Samsung a repris la logique derrière le procédé « GAAFET » pour développer le « MBCFET » (Multi-Bridge-Channel FET).

Des nanofeuilles à la place de nanofils chez Samsung

Avec succès, se vante le fondeur sud-coréen, car les limites de performance du FinFET sont dépassées, que ce soit en matière d’efficacité énergétique et de performances. Le secret ? Les nanofils sont remplacés par des nanofeuilles, qui conduisent encore mieux le courant électrique. Il s’agit d’une technologie exclusive, souligne Samsung.

Ici, des nanofeuilles avec des canaux plus larges sont mises en œuvre pour arriver aux performances mentionnées précédemment. Les nanofils et leurs canaux plus étroits sont remplacés et le fondeur prévient qu’il est aussi en mesure de moduler la largeur du canal « afin d’optimiser l’utilisation de l’énergie et les performances pour répondre aux différents besoins des clients ».

Les travaux de Samsung illustrent bien le fait que la course à la miniaturisation s’est quelque peu heurtée à un mur technologique et que les industriels sont obligés d’inventer des approches originales pour continuer à améliorer les processeurs. Les FinFET, GAAFET et MBCFET en sont la démonstration la plus éclatante. Et Olivier Faynot ne disait pas autre chose :

« La terminologie employée ne correspond plus forcément à une dimension mesurée sur le circuit intégré. Historiquement, quand on parlait d’un nœud à 28 nm, cette valeur reflétait une grandeur physique, à savoir la longueur de la grille du transistor. Désormais, quand un industriel évoque un nœud de 5 ou 7 nm, les dimensions sont plutôt de l’ordre de 10 nm. »

« Il est largement reconnu dans l’industrie que la nomenclature nanométrique est incohérente et confuse et qu’elle ne reflète pas les dernières innovations au niveau des transistors », déclarait aussi Chelsea Hughes, porte-parole d’Intel. Mais il est parfois difficile de se départir du marketing, puisque le groupe évoquait le passage à « l’ère angström » — c’est-à-dire sous le nanomètre.

+ rapide, + pratique, + exclusif

Zéro publicité, fonctions avancées de lecture, articles résumés par l'I.A, contenus exclusifs et plus encore.

Découvrez les nombreux avantages de Numerama+.

Vous avez lu 0 articles sur Numerama ce mois-ci

Tout le monde n'a pas les moyens de payer pour l'information.

C'est pourquoi nous maintenons notre journalisme ouvert à tous.

Mais si vous le pouvez,

voici trois bonnes raisons de soutenir notre travail :

- 1 Numerama+ contribue à offrir une expérience gratuite à tous les lecteurs de Numerama.

- 2 Vous profiterez d'une lecture sans publicité, de nombreuses fonctions avancées de lecture et des contenus exclusifs.

- 3 Aider Numerama dans sa mission : comprendre le présent pour anticiper l'avenir.

Si vous croyez en un web gratuit et à une information de qualité accessible au plus grand nombre, rejoignez Numerama+.

Toute l'actu tech en un clin d'œil

Ajoutez Numerama à votre écran d'accueil et restez connectés au futur !

Tous nos articles sont aussi sur notre profil Google : suivez-nous pour ne rien manquer !